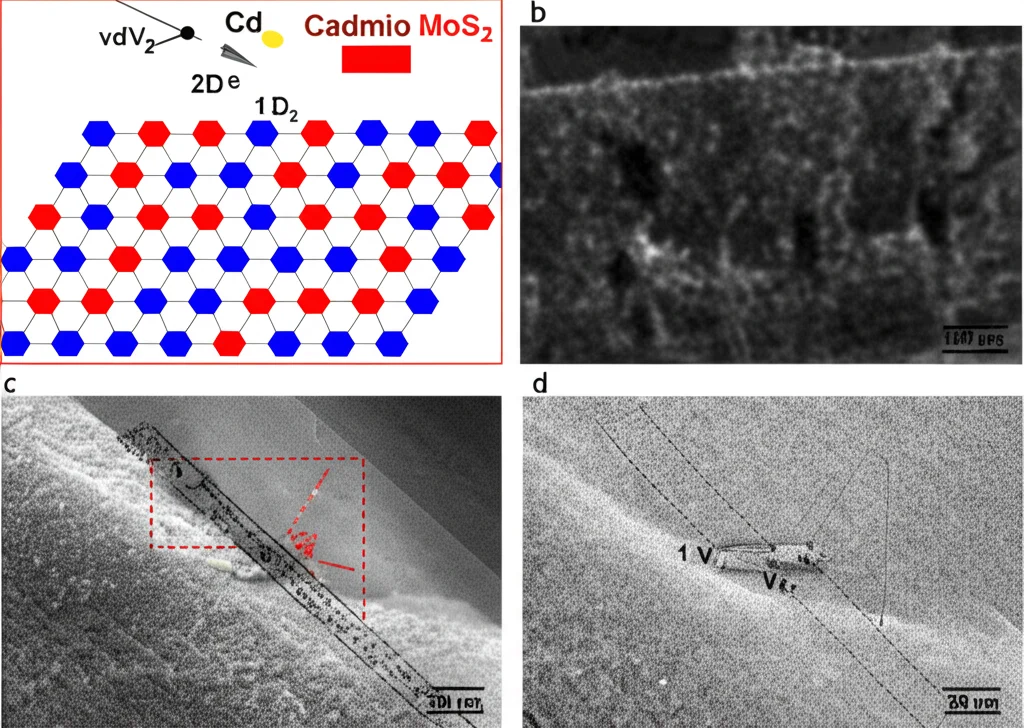

Contatti Metallici 2D al Cadmio: Rivoluzioniamo i Transistor con l’Epitassia van der Waals!

Ciao a tutti, appassionati di scienza e tecnologia! Oggi voglio parlarvi di qualcosa che mi entusiasma da matti: il futuro dell’elettronica. Siamo onesti, il nostro caro vecchio silicio, protagonista indiscusso per decenni grazie alla legge di Moore, sta iniziando a mostrare la corda. Rimpicciolire ancora i transistor diventa sempre più difficile. Ma ecco che entrano in gioco loro: i materiali bidimensionali (2D)! Sottili come un singolo strato di atomi, promettono prestazioni elettriche superiori al silicio, specialmente su scale minuscole. Sembrano la risposta perfetta per l’elettronica “oltre il silicio”.

Il Tallone d’Achille: I Contatti Elettrici

C’è un “ma” grande come una casa, un problema che ci fa sudare freddo da tempo: realizzare contatti elettrici efficienti con questi materiali 2D. È un po’ come cercare di collegare un cavo super sottile a una presa enorme senza perdite o interferenze. Il problema principale è l’elevata resistenza di contatto (RC) e la formazione di una fastidiosa barriera di Schottky all’interfaccia tra il metallo del contatto e il semiconduttore 2D.

Questa barriera nasce principalmente per due motivi, che in gergo chiamiamo:

- MIGS (Metal-Induced Gap States): Stati elettronici indesiderati che si formano quando gli elettroni del metallo “invadono” la banda proibita del semiconduttore.

- DIGS (Defect-Induced Gap States): Difetti creati proprio durante i processi tradizionali usati per fabbricare i contatti, come la litografia e la deposizione dei metalli.

Questi processi, diciamocelo, sono spesso brutali: usano alte energie, possono danneggiare la delicatissima struttura atomica dei materiali 2D e lasciano residui indesiderati. Anche tecniche più recenti, come il trasferimento di elettrodi pre-fabbricati, rischiano di introdurre contaminanti, bolle o pieghe all’interfaccia. Insomma, ottenere un contatto pulito e perfetto è una vera sfida. E le alte temperature richieste da alcuni metodi sono incompatibili con le fasi finali di produzione dei chip (il cosiddetto BEOL, Back-End-Of-Line), che richiedono temperature sotto i 400 °C.

La Nostra Idea: Epitassia van der Waals a Bassa Temperatura con il Cadmio!

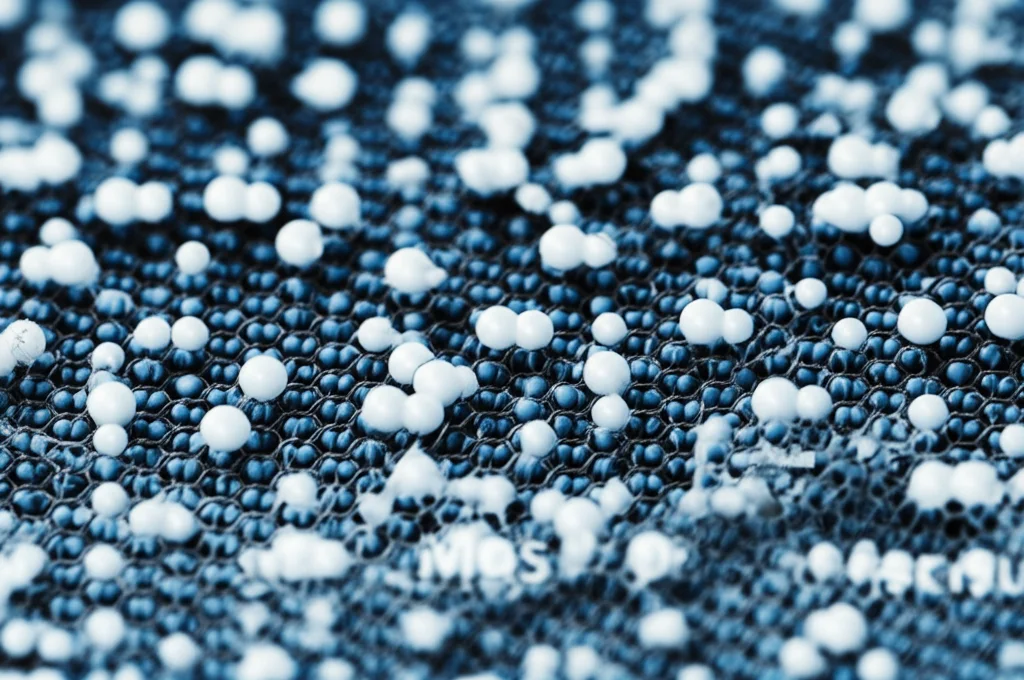

E se potessimo aggirare tutti questi problemi? Se potessimo “far crescere” il contatto metallico direttamente sul materiale 2D, in modo dolce, pulito e a bassa temperatura, sfruttando le stesse forze deboli (le forze di van der Waals, vdW) che tengono insieme gli strati di questi materiali? È qui che entra in gioco la nostra strategia: l’epitassia vdW a bassa temperatura.

Abbiamo scelto un metallo forse inaspettato: il Cadmio (Cd). Perché proprio il Cadmio? Per tre ottimi motivi:

- Funzione Lavoro Ideale: La sua “funzione lavoro” (un parametro che indica l’energia necessaria per strappare un elettrone dal metallo) è quasi identica all’affinità elettronica del MoS₂ (uno dei materiali 2D più studiati). Questo significa, in teoria, una barriera di Schottky minima, quasi zero!

- Crescita Perfetta e Meno “Disturbi”: Simulazioni al computer (DFT) ci hanno mostrato che il Cd tende a crescere in modo ordinato, piano su piano (Cd(001) su MoS₂(001)), formando un’interfaccia vdW pulitissima. Inoltre, il Cd “disturba” meno la struttura elettronica del MoS₂, riducendo drasticamente i famigerati MIGS.

- Basso Punto di Fusione: Il Cadmio fonde a soli 321 °C, il che ci permette di farlo crescere tramite deposizione chimica da vapore (CVD) a temperature bassissime (attorno ai 108 °C sul substrato!), perfettamente compatibili con i processi BEOL e senza danneggiare il materiale 2D sottostante.

Il bello di questo approccio è che elimina completamente la necessità di litografia e deposizione tradizionale per formare i contatti. Facciamo crescere delle “isole” esagonali di Cd sul MoS₂; controllando tempo e temperatura, queste isole si espandono fino quasi a toccarsi, lasciando un piccolo spazio vuoto (il “canale” del transistor) tra di loro, con lunghezze che possiamo controllare da poche decine a centinaia di nanometri.

Guardare da Vicino: Un’Interfaccia da Sogno

Abbiamo usato tutte le tecniche di caratterizzazione più avanzate per “spiare” questa interfaccia Cd-MoS₂: microscopia a forza atomica (AFM), microscopia a sonda Kelvin (KPFM), microscopia elettronica a scansione (SEM), spettroscopia Raman e fotoluminescenza (PL), diffrazione elettronica (SAED), diffrazione a raggi X (XRD), spettroscopia fotoelettronica a raggi X (XPS) e, soprattutto, la microscopia elettronica a trasmissione a scansione ad alto angolo (HAADF-STEM).

I risultati sono stati sbalorditivi! Le immagini STEM mostrano un’interfaccia atomicamente netta e pulita, senza difetti indotti dal metallo, senza mescolamento atomico. Il Cd cresce proprio come previsto dalle simulazioni, con il piano (001) parallelo a quello del MoS₂. Abbiamo misurato una distanza vdW tra gli atomi di Zolfo (S) del MoS₂ e gli atomi di Cd di appena 1.06 Ångström (un decimo di miliardesimo di metro!). È una delle distanze più piccole mai riportate, segno di un contatto vdW quasi ideale, molto migliore di quelli ottenuti con tecniche di trasferimento o deposizione tradizionale. Le altre analisi confermano che il MoS₂ sottostante rimane intatto, senza danni chimici o strutturali. È l’interfaccia termodinamicamente stabile e pulita che sognavamo!

Prestazioni da Urlo: I Transistor Cd-MoS₂ al Test

Ma la prova del nove è sempre la stessa: come funzionano i dispositivi? Abbiamo fabbricato dei transistor a effetto di campo (FET) usando il MoS₂ come canale e le nostre isole di Cd cresciute epitaxialmente come contatti di source e drain. I risultati? Semplicemente eccezionali.

Ecco qualche numero per darvi un’idea:

- Resistenza di Contatto (RC) bassissima: Tra 70 e 100 Ω·μm. Un valore incredibilmente basso!

- Corrente On-State Elevatissima: Fino a 788 μA/μm per canali da 100 nm e addirittura 942 μA/μm per canali da 50 nm!

- Rapporto On/Off stratosferico: Superiore a 10⁸ (cento milioni!). Questo significa che il transistor “spegne” benissimo, consumando poca energia.

- Mobilità dei portatori elevata: Fino a 160 cm²V⁻¹s⁻¹. Un indicatore della “velocità” degli elettroni nel canale.

- Barriera di Schottky quasi zero: Le misure confermano un contatto ohmico quasi perfetto, senza barriera apprezzabile.

- Isteresi minima: Solo 112 mV/(MV cm⁻¹). L’isteresi è un effetto indesiderato che indica la presenza di stati trappola all’interfaccia; un valore così basso è sintomo di un’interfaccia pulitissima.

Abbiamo confrontato questi risultati con transistor MoS₂ realizzati con contatti tradizionali in Cromo/Oro (Cr/Au). Non c’è paragone: i nostri dispositivi Cd-MoS₂ hanno un rapporto on/off 1000 volte migliore, una corrente on-state 30 volte più alta, una mobilità nettamente superiore e un’isteresi enormemente ridotta. Abbiamo anche confrontato con altre tecniche avanzate, come l’uso di elettrodi trasferiti o di semimetalli depositati (come il Bismuto, Bi): i nostri contatti epitassiali in Cd si sono dimostrati superiori.

Stabilità e Affidabilità

Non solo prestazioni da record, ma anche stabilità. I nostri dispositivi hanno resistito a test termici fino a 570 K (quasi 300 °C) senza degradazioni significative e hanno mostrato proprietà elettriche quasi invariate dopo 60 giorni. Anche sotto stress elettrico, il Cd 2D si è dimostrato robusto. La bassa isteresi e la ridotta corrente di leakage (perdita) confermano ulteriormente la qualità superiore dell’interfaccia vdW ottenuta con la nostra tecnica.

Le simulazioni TCAD (Technology Computer-Aided Design) ci hanno aiutato a capire meglio perché questi contatti funzionano così bene. Grazie alla bassa barriera, il campo elettrico all’interno del canale del transistor è molto più uniforme rispetto ai contatti tradizionali. Questo riduce picchi di campo localizzati, migliora la risposta lineare della corrente e diminuisce le perdite energetiche e lo scattering (la “deviazione” degli elettroni) durante il trasporto. Anche effetti indesiderati tipici dei canali corti, come la modulazione della lunghezza del canale, sono risultati molto meno pronunciati nei nostri dispositivi. L’analisi statistica su decine di dispositivi ha confermato l’elevata uniformità e le prestazioni superiori rispetto ai metodi convenzionali.

Non Solo MoS₂: Una Strategia Universale?

Per dimostrare che non si tratta di un caso fortunato limitato al MoS₂, abbiamo applicato la stessa tecnica di crescita epitassiale del Cd su un altro importante materiale 2D: il disolfuro di tungsteno (WS₂). Anche in questo caso, i transistor Cd-WS₂ hanno mostrato prestazioni nettamente superiori rispetto ai contatti tradizionali, confermando la potenziale universalità del nostro approccio.

Verso il Futuro dell’Elettronica

In conclusione, la nostra tecnica di epitassia vdW a bassa temperatura per crescere contatti metallici 2D in Cadmio direttamente sui semiconduttori 2D rappresenta un passo avanti significativo. Offre interfacce atomicamente pulite, minimizza i danni, sopprime gli stati interfacciali indesiderati (MIGS e DIGS) e permette di ottenere transistor con prestazioni eccezionali: bassa resistenza, alta corrente, alta velocità, basso consumo e grande stabilità.

Questi risultati non sono solo eccitanti dal punto di vista scientifico, ma aprono una strada concreta verso la realizzazione di transistor 2D ad alte prestazioni che potrebbero un giorno complementare, competere o addirittura superare l’elettronica basata sul silicio. Le prestazioni che abbiamo ottenuto soddisfano già alcuni degli obiettivi più ambiziosi delle roadmap tecnologiche internazionali (ITRS e IRDS) per i transistor 2D. Il futuro dell’elettronica potrebbe essere davvero… piatto e brillante!

Fonte: Springer